2022. 10. 29. 07:46 devel/개념

RH850G3KH core Interrupt Handler에 대하여

결론부터 요약

Direct Vector Method

- EIIC 값 확인

- Exception Cause(EIINTn) = EIIC – Exception Cause Code Base Address

- EIINT Offset = EIINTn x 0x10 + 0x100

- RBASE 혹은 EBASE + EIINT Offset

RINT가 0이라고 가정, RINT가 1이면 걍 0x100임

자! 이제 어떻게 인터럽트 핸들러가 실행되는 걸까? 상세 설명을 보시라

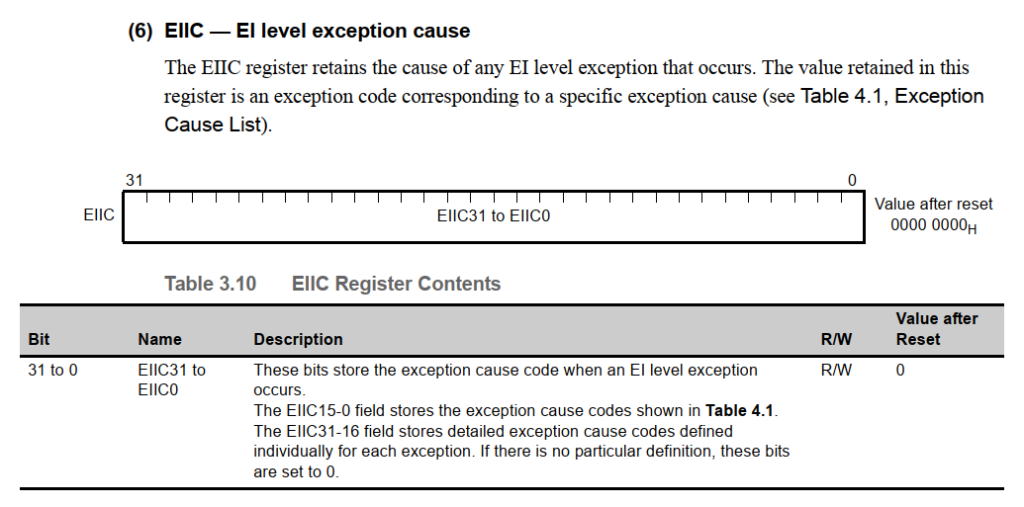

A. 장치로 인터럽트가 들어왔다고 치자. 그러면 EIIC 라는 레지스터에 Exception Cause Code가 뜬다.

B. Exception Cause(EIINTn) = EIIC value – Exception Cause Code Base Address

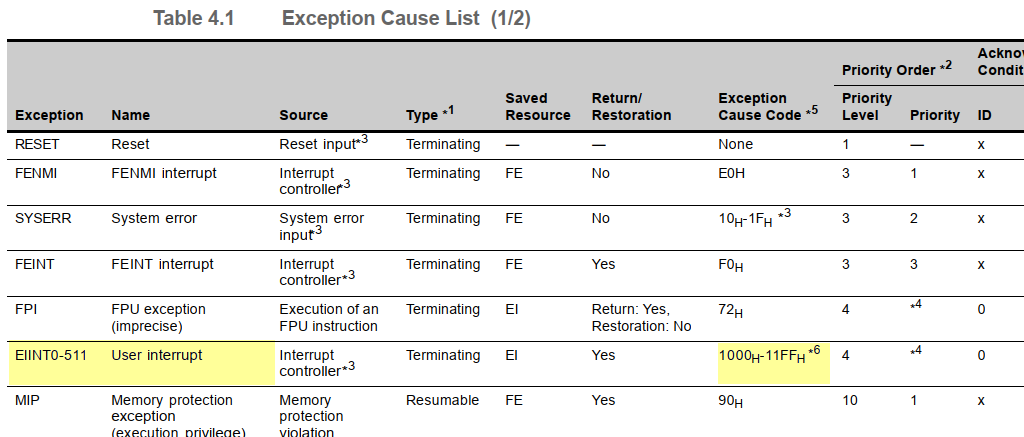

User Int라고 가정하자. 아래 표를 보면 EIINT 0 – 511까지 총 512개가 있고 Exception Cause Code는 0x1000 – 0x11FF임을 알 수 있다. 즉 Exception Cause Code Base Address이 0x1000이다. (당연한 내용이지만 0x11FF – 0x1000 = 0x200 즉 512)

만약 EIIC에 값이 0x1007로 들어왔다면 EIIC Offset = 0x1007 – 0x1000 = 7임을 알 수 있다.

아래는 그냥 참고용이다 Exception Cause Code의 시작 주소가 각기 다른 것을 확인하시라

C. EIINTn Offset 을 구해보자

EIINTn priority 0이 0x100부터 시작이다. 그러니까 아까 예시의 7번은 0x170이 되겠다

이걸 공식화 하면 0x100 + Exception Cause x 0x10

D. 마무리

PSW.EBV 값에 따라 RBASE 혹은 EBASE 값에 이전 단계에서 구한 EIINTn Offset을 더하면 끝

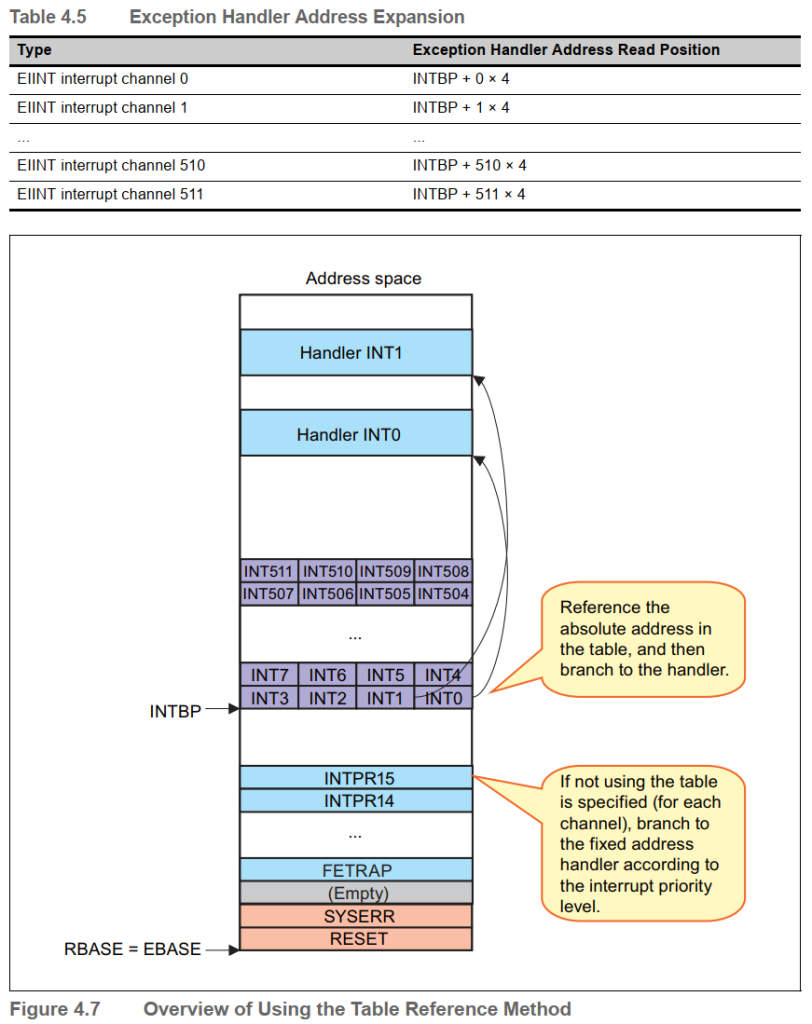

Table Reference Method는요?

설명하기 귀찮다

INTBP + Exception Cause x 4 하면 된다.

startup 코드에서 미리 INTBP 설정하는 거 잊지 말고오오~~~~

'devel > 개념' 카테고리의 다른 글

| ChatGPT한테 배운 코딩 패턴 (2) | 2024.12.19 |

|---|---|

| Renesas RH850G3KH core의 barrier에 관해 (0) | 2022.10.10 |

| RH850G3KH core exception/interrupt 관련 정리 (1) | 2022.10.03 |

| ARM Cortex-M Programming Guide to Memory Barrier Instructions (0) | 2018.03.25 |

| 아마존 리눅스 서버 최적화 튜닝 (0) | 2017.11.15 |