2022. 10. 10. 18:01 devel/개념

Renesas RH850G3KH core의 barrier에 관해

cortex 시리즈도 그렇고 pipeline은 기본 탑재 되어있다.

pipeline에 대한 개념은 대충 다 알고 있으리라 본다.

pipeline에 대한 이해는 정말 간단한 프로그램을 어셈으로 짜놓고 nop 최적화 같은거 하면 정말 쉽게 깨닫게 된다.

이 작업을 하고 있으면 뭔가 자신이 굉장히 하이테크의 정점에 다가선듯한 기분을 체험해볼 수 있으며 그 날은 이야 내가 인생을 허비한 것이 아니라 제대로 살았구나라고 머리속 모든 것이 긍정적으로 변하는 그런 날이 될 수 있다.

바로 직전에 롤에서 10데스하는 핵트롤을 하다가 도저히 오늘은 게임 하는 날이 아닌가보다 하고 공부를 시작했다고 하더라도 말이다.

여튼 pipeline에 의해 barrier 가 필요하다.

이걸 Renesas에서는 어떻게 제공하고 있는가?

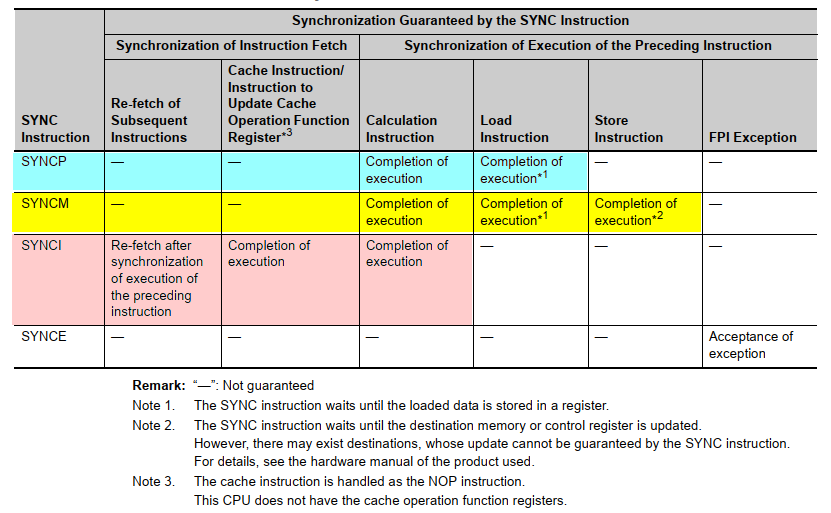

SYNCE는 FPI 소수점 관련 내용

SYNCI는 instruction(Synchronize memory for instruction writers)

SYNCM은 memory(memeory, register) load/store

SYNCP는 memory load만(synchronize pipeline)

SYNCI 항목에는 Calculation Instruction이라고 적혀있는데 Appendix A를 보면 연산과 관련된 작업 외 PSW, MPU 등 기타 시스템 관련 레지스터 작업 관련해서도 보장함을 알 수 있다.

'devel > 개념' 카테고리의 다른 글

| ChatGPT한테 배운 코딩 패턴 (2) | 2024.12.19 |

|---|---|

| RH850G3KH core Interrupt Handler에 대하여 (0) | 2022.10.29 |

| RH850G3KH core exception/interrupt 관련 정리 (1) | 2022.10.03 |

| ARM Cortex-M Programming Guide to Memory Barrier Instructions (0) | 2018.03.25 |

| 아마존 리눅스 서버 최적화 튜닝 (0) | 2017.11.15 |