2022. 10. 3. 16:14 devel/개념

RH850G3KH core exception/interrupt 관련 정리

르네사스에 대한 정보가 아예 없어 안타까워서 정리해본다.

나도 잘 모르는 내용이다. 간단하게 인터럽트 핸들러 설정 관련 글을 정리해본다.

틀렸는데요? -> 아주 좋은 지적이다. 좀 자세히 알려다오.

근데 생각해보니까 르네사스 칩의 메뉴얼을 봐야할 정도면 굳이 이런 내용 없어도 알아서 다 파악할 수 있는 능력을 가졌을텐데 내가 여기에 이런걸 적고 있는게 의미가 있는걸까 급 후회가 되기도 하지만 블로그에 헛소리가 너무 많으니 그걸 치우기 위해 뭔가 있어보이는 내용을 적어본다.

아래의 내용은 REN_r01us0165ej0120-rh850g3kh_MAS_20171026.pdf 라는 전혀 직관적이지 않은 더러운 파일명을 가진 메뉴얼을 요약한 것이다.

그냥 홈페이지에 회원 가입해서 다운 받을 수 있는 파일이다.

Basic System Register들 중에 여러가지가 있겠다만 PSW라는 놈이 있다.

ARM도 이런놈 있는거 알쟤?

PSW(Program Status Word)

현재 instruction execution result를 기록해두는 즉 status flag들을 모아둔 register

15번째 bitfield가 EBV

EBV

reset vector, exception vector 동작 관련 flag

RBASE, EBASE와 연관이 있다.

데이터 시트 뭐의 약자인지 안 나와있다. Exception Base Vector?

Exception

unusual event 즉 CPU 입장에서 아...나는 이제 망했구나 진짜 큰 일이 발생했구나 싶을 때 발생하는 이벤트

exception handler가 발동 된다.

언제 발생하는지에 대한 예시 목록이 있는데 예를 들면 뭐 이렇다.

Reset 발생하면 Reset 이라는 Exception이 발생하고 FPU exception, User Interrupt Exception, System Error, Memory Protection Exception 등등

FENMI, FEINT, EIINT 이런 중요한 3형제가 있는데 일단 넘어가자 여기서 힘 다 빼면 안된다

Interrupt Priority Order & Mask

일단 넘어가자

대충 어떤 개념인지는 알 것이라 생각된다.

뭔가 어떤 값을 설정하면 Priority 가 있고 Masking으로 인터럽트 허용 여부를 결정할 수 있겠지

집중력을 아껴야 한다

Exception Handler Address

서론 끝나고 드디어 도착 이제부터 중요하다.

높은 성능 향상 목적을 위해 이렇게 디자인 했다고는 하는데 진짜 왜 이렇게 디자인 했을까 싶은 생각이 드는 파트인데 뭔가 다 이유가 있지 않을까 아직 내가 시야가 좁아서 그런건가 싶은 부분이다. 일단 내용을 그대로 옮겨보자.

exception이 발생하면 handler를 실행해야 한다.

이 handler의 address는 2가지 방법이 있다.

1. Direct Vector Method

2. Table Reference Method

A. Direct Vector Method

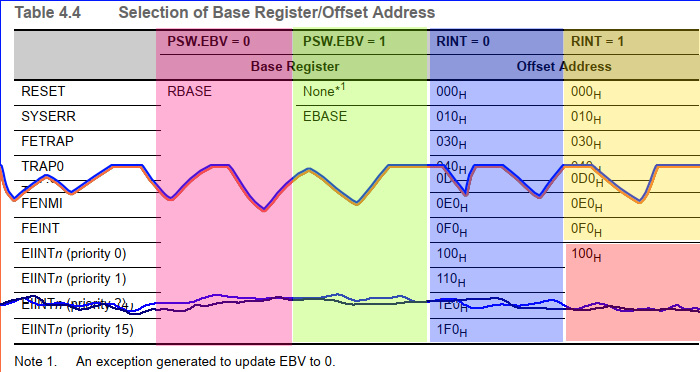

CPU는 exception cause offset + Base Address 를 사용한다.

exception cause offset이라는건 exception list 가 표로 있는데 각 exception의 원인(cause)마다 offset이 할당 되어 있다.

위의 표가 전부다.

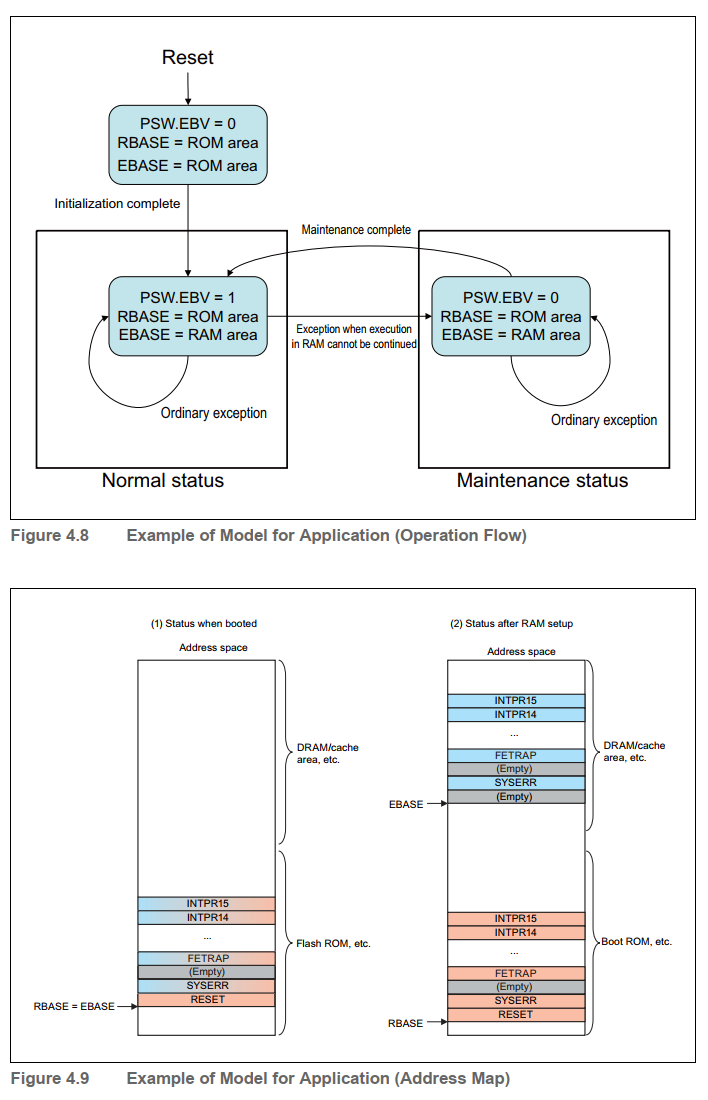

PSW.EBV 의 값에 따라 BASE address를 RBASE/EBASE register에서 참조할지

그리고 RINT(RBASE/EBASE 내부에 있는 flag)의 값에 따라 offset이 결정된다.

위의 표가 이해 된다면 이하의 글은 읽지 않고 그냥 넘어가도 ok

Base Address

PSW.EBV = 0 : RBASE에 있는 address

PSW.EBV = 1 : EBASE에 있는 address

주의 사항: 몇몇의 exception은 항상 RBASE를 사용한다.

RINT는 R/EBASE에 있는 bitfield인데 이 flag가 1인 경우 EIINT (user interrupt)가 0x100 offset 주소로 handling 된다.

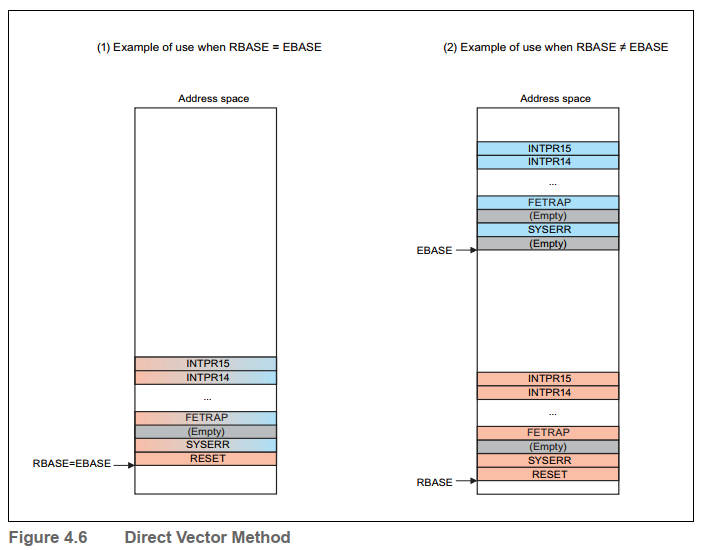

RBASE의 주소와 EBASE의 주소는 동일하게 설정할 수도 있고 다르게 설정할 수도 있다.

아래 그림의 INTPRx는 EIINTn과 같다

RINT = 1의 용도 : user interrupt 를 모두 0x100에서 처리하기 때문에 특정 상황에서 메모리를 적게 사용할 수 있다.

B. Table Reference Method

direct vector method는 각 interrupt priority level마다 하나의 user interrupt exception handler를 사용할 수 밖에 없음

여러 인터럽트와 연결된 채널은 동일한 priority와 같은 handler를 사용할 수 밖에 없음

이 문제를 해결해주는 방법임

direct vector method가 사용 되는 케이스

1. PSW.EBV = 0 && RBASE.RINT = 1

2. PSW.EBV = 1 && RBASE.RINT = 1

3. 인터럽트 채널 세팅이 Table Reference Method로 설정 되어있지 않음

위의 케이스 외는 table reference method로 동작한다.

Table Reference Method의 handler address = INTBP register + 채널 offset 내부의 값(int 채널 번호 x 4Bytes)

아래의 그림이 더 쉬운 이해를 도와줄 것이다.

INTBP부터 시작해서 레지스터들이 엄청나게 많은데(거의 뭐 메가 단위?) 거기에 각 interrupt handler 주소를 넣어서

세팅할 수 있음

그래서 exception이후 interrupt handler 동작이 조금 느림

exception -> table reference를 함(INBTP + 채널 offset)의 레지스터 값을 read -> 그 값이 handler가 있는 곳이므로 그곳으로 이동

C. 그러면 왜 디자인을 이렇게 나누었는가? 용도는?

다음주에 추가해보도록 하겠다.

더이상 에너지가 없다.

그림으로 상상 해보자

'devel > 개념' 카테고리의 다른 글

| RH850G3KH core Interrupt Handler에 대하여 (0) | 2022.10.29 |

|---|---|

| Renesas RH850G3KH core의 barrier에 관해 (0) | 2022.10.10 |

| ARM Cortex-M Programming Guide to Memory Barrier Instructions (0) | 2018.03.25 |

| 아마존 리눅스 서버 최적화 튜닝 (0) | 2017.11.15 |

| 주소가 주어진 영역 이내인지 확인 하는 방법 (0) | 2017.10.01 |