2023. 9. 13. 22:30 devel/etc

Tricore 1.6 아키텍쳐 공부#1

tricore 아키텍쳐에 대해 써보려고 한다.

정확히 벤치를 돌려보지는 않았는데 체감 성능은 Cortex M7은 가야 맞짱이 가능하지 않나 싶다.

벤치를 돌려본게 아니라 진짜 성능이 그렇게 나오는지는 모르것고 일단 줜나 빠르고 줜나....비싸다.

Aurix 3G TC4x 시리즈 나오면 가격이 얼마나 갈까

시간 되면 V850

여튼 tricore에 대해 설명해둔 자료도 없고 공부하는 식으로 정리를 해보려고 한다.

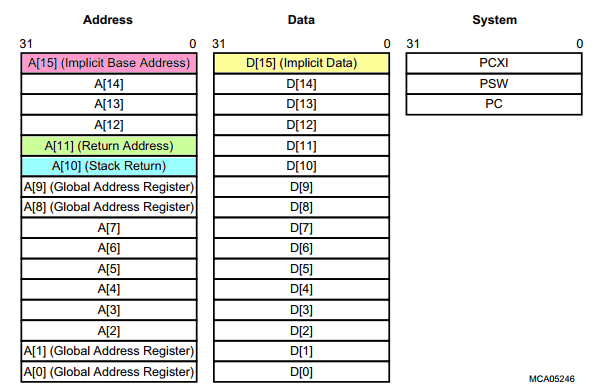

레지스터

The PCXI, PSW and PC registers are crucial to the procedure for storing and restoring a task’s context

PCXI - Previous Context Information register

PSW -Program Status Word

Registers [0H - 7H] are referred to as the ‘lower registers’

and registers [8H - FH] are called the ‘upper registers’.

Registers A[0], A[1], A[8], and A[9] are defined as system global registers.

These are not included in either the upper or lower context

and are not saved and restored across calls or interrupts.

They are normally used by the operating system to reduce system overhead

그럼 그냥 스크래치 용으로 써도 되는건가?

Memory Model

The architecture can access up to 4 GBytes (address width is 32-bits) of unified program and I/O memory. The address space is divided into 16 regions or segments [0H - FH], each of 256 MBytes. The upper four bits of an address select the specific segment.

Tasks and Contexts

A task is an independent thread of control. There are two types: Software Managed Tasks (SMTs) and Interrupt Service Routines (ISRs).

그냥 task 수행되는 걸 SMT라고 하고 인터럽트 처리되는 건 ISR이라고 하나보다

근데 왜 하필 이름을 SMT라고......

SMT는 당연히 여러가지 모드가 있다.

User-0 Mode

Used for tasks that do not access peripheral devices. This mode cannot enable or disable interrupts.

신기하네요. ARM Cortex에는 이런식으로 제한된 모드가 없어요. MPU를 써서 뭐 막아부리는게 아니면

User-1 Mode

Used for tasks that access common, unprotected peripherals. Typically this would be a read orwrite access to serial port, a read access to timer, and most I/O status registers. Tasks in this mode may disable interrupts for a short period.

Supervisor Mode

Permits read/write access to system registers and all peripheral devices. Tasks in this mode may disable interrupts

Individual modes are enabled or disabled primarily through the I/O mode bits in the Processor Status Word (PSW).

Context Save Areas

아...이런 이름 쓰지 말지. 타사의 HW랑 너무 중복 되네요 Save Area 이런거 용어로 쓰지 말자

The architecture uses linked lists of fixed-size Context Save Areas (CSAs). A CSA consists of 16 words of memory storage(64Bytes ㄷㄷㄷ), aligned on a 16-word boundary. Each CSA can hold exactly one upper or one lower context. CSAs are linked together through a Link Word

upper/lower context라는 용어가 나왔는데 일단 넘어가자

Context switching occurs when an event or instruction causes a break in program execution. The CPU then needs to resolve this event before continuing with the program.The events and instructions which cause a break in program execution are :

• Interrupt or service requests

• Traps

• Function calls

'devel > etc' 카테고리의 다른 글

| Tricore 1.6 아키텍쳐 공부#2 (1) | 2023.11.29 |

|---|---|

| 집에서 숯불구이 해본 후기 - 결론: 하지마 (1) | 2023.05.28 |

| 메인보드 구매할 때 블루투스 기능이 과연 필요할까? (0) | 2022.01.09 |

| 텐키리스 키보드 사용 짧은 후기(개발자) (0) | 2022.01.09 |

| 윈도우에서 배치파일, makefile로 빌드 시스템 구축하기 (0) | 2021.02.16 |